MÜHENDİSLİK FAKÜLTESİ FACULTY OF ENGINEERING ELEKTRİK-ELEKTRONİK MÜHENDİSLİĞİ BÖLÜMÜ DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

DUMLUPINAR BULVARI 06800 ÇANKAYA ANKARA/TURKEY T: +90 312 210 23 02 F: +90 312 210 23 04 ee@metu.edu.tr www.eee.metu.edu.tr

# **EXPERIMENT 1. INTRODUCTION TO ALTERA**

# I. Introduction

### I.I Objectives

In this experiment, you will learn computer aided digital design and verification of it using Field Programmable Gate Arrays (FPGA). For programmable logic design, you will learn how to use Quartus II 14.1 software tools.

### I.II. Background: Implementation of a logic function with standard gates

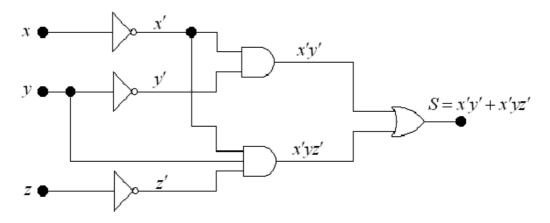

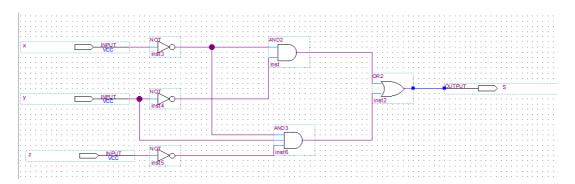

Let us design a combinational circuit with three inputs and one output. The output is equal to logic-1 when binary value of the input is less than 3. The output is logic-0 otherwise. Table 1 shows the truth table for this logic function, where x, y, z are the inputs and S is the output. Figure 1 shows the schematic diagram of the designed combinational circuit.

Table 1. Truth table of the design

| Х | у | Z | S |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

S = x'y'z' + x'y'z + x'yz'  $S = x'y'(z'+z) + x'yz' \text{ since } (z'+z) = 1 \text{ and } \mu \cdot 1 = \mu$ S = x'y' + x'yz'

Experiment 1: Introduction to ALTERA by Eren Aydın and Barış Bayram © 2015 All Rights Reserved. (e-mail: <u>ernaydn@gmail.com</u>)

Fig. 1: Logic diagram of the design

### **II. Preliminary Work**

- **1)** Read the document about ESD and briefly explain your understanding in less than 250 words. (what is ESD, effects of ESD, how to protect from ESD etc...)

- **2)** Read the document about FPGA and explain what FPGA is, applications and limitations in less than 250 words.

- **3)** Read the Background information of the experiment, design an alternative circuit other than the circuit shown in the Fig. 1.

Hint:

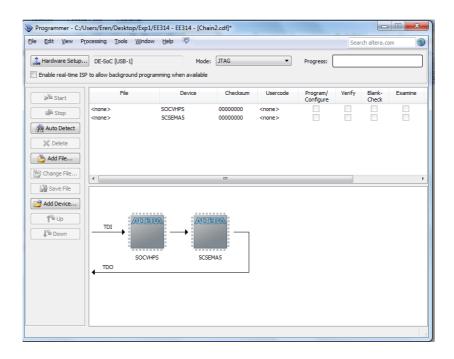

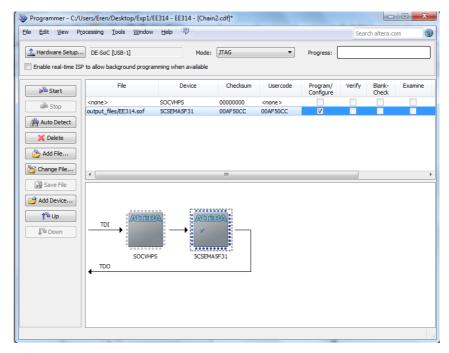

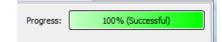

**4)** Bring an at least 8 GB USB to EA314 (or download Quartus II 14.1 web edition) and take the installation files from Yeşim Yücesan in EA 314 during the week. Install Quartus II 14.1 to your computer, and do the tutorial given to you until the end of page 31 (Programming and Configuring the FPGA Device). **Include the screenshots to show that you fulfilled this task fully and completely.**

### **III. Experimental Work**

- a) Starting a New Project

- **1)** Create a directory on your desktop with the name of Exp1.

- **2)** Double click on the Quartus II 14.1 icon on your desktop.

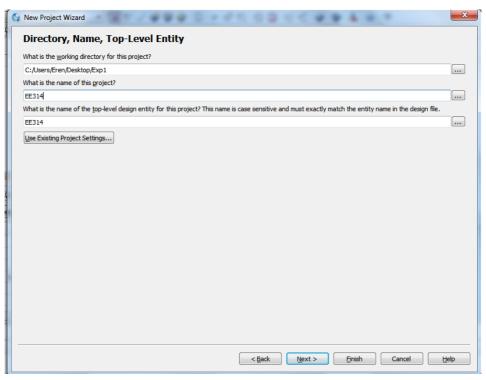

- **3)** After opening Quartus II 14.1, you will start a new project. **Select File>New Project Wizard** and click **Next** in the opening window. In the new window set the working directory as Exp1 and write the project name as EE314 as seen from the Figure 2 then click **Next**.

Fig. 2: Assigning working directory and project name

### 4) Choose **Empty Project** and click **Next**.

### 5) Click Next.

**6)** Choose Device Family as **Cyclone V** and Choose **5CSEMA5F31C6** (for DE1-SoC) from the list and click **Next**.

| •                          |

|----------------------------|

| •                          |

|                            |

| •                          |

|                            |

|                            |

|                            |

| PCIe Hard IP Block         |

| PCIe Hard IP Block         |

|                            |

| 0                          |

| 0                          |

| 0<br>0<br>0                |

| 0<br>0<br>0<br>0<br>0      |

| 0<br>0<br>0<br>0<br>0      |

| 0<br>0<br>0<br>0<br>0<br>0 |

|                            |

Fig. 3: Device Selection Window

- 7) Click Next.

- **8)** A summary window will be visible. The summary window should be similar to the Fig. 4. Click **Finish**.

| Summary         When you click Finish, the project will be created with the following settings:         Project directory:       C:/Users/Eren/Desktop/Exp1         Project name:       EE314         Top-level design entity:       EE314         Number of files added:       0         Device assignments:       0         Design template:       n/a |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| When you click Finish, the project will be created with the following settings:         Project directory:       C:/Users/Eren/Desktop/Exp1         Project name:       EE314         Top-level design entity:       EE314         Number of files added:       0         Number of suer libraries added:       0         Device assignments:            |      |

| Project directory:     C:/Users/Eren/Desktop/Exp1       Project name:     EE314       Top-level design entity:     EE314       Number of files added:     0       Number of suer libraries added:     0       Device assignments:                                                                                                                        |      |

| Project name:     EE314       Top-level design entity:     EE314       Number of files added:     0       Number of user libraries added:     0       Device assignments:                                                                                                                                                                                |      |

| Top-level design entity:     EE314       Number of files added:     0       Number of user libraries added:     0       Device assignments:     0       Design template:     n/a                                                                                                                                                                         |      |

| Number of files added:     0       Number of user libraries added:     0       Device assignments:     0       Design template:     n/a                                                                                                                                                                                                                  |      |

| Number of user libraries added:     0       Device assignments:                                                                                                                                                                                                                                                                                          |      |

| Device assignments:<br>Design template: n/a                                                                                                                                                                                                                                                                                                              |      |

| Design template: n/a                                                                                                                                                                                                                                                                                                                                     |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

| Family name: Cyclone V (E/GX/GT/SX/SE/ST)                                                                                                                                                                                                                                                                                                                |      |

| Device: 5CSEMA5F31C6                                                                                                                                                                                                                                                                                                                                     |      |

| EDA tools:                                                                                                                                                                                                                                                                                                                                               |      |

| Design entry/synthesis:  ( <none>)</none>                                                                                                                                                                                                                                                                                                                |      |

| Simulation: ModelSim-Altera (VHDL)                                                                                                                                                                                                                                                                                                                       |      |

| Timing analysis: 0                                                                                                                                                                                                                                                                                                                                       |      |

| Operating conditions:                                                                                                                                                                                                                                                                                                                                    |      |

| Core voltage: 1.1V                                                                                                                                                                                                                                                                                                                                       |      |

| Junction temperature range: 0-85 °C                                                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

|                                                                                                                                                                                                                                                                                                                                                          |      |

| < Back Next > Finish Cancel                                                                                                                                                                                                                                                                                                                              | Help |

Fig. 4: Summary Window

# **b)** Entering The Design

- 1) Choose File>New >Block Diagram/Schematic File and click OK. Then Choose File>Save as and enter the name of the file as EE314. Ensure that "Add the file to current project" is selected and then click Save.

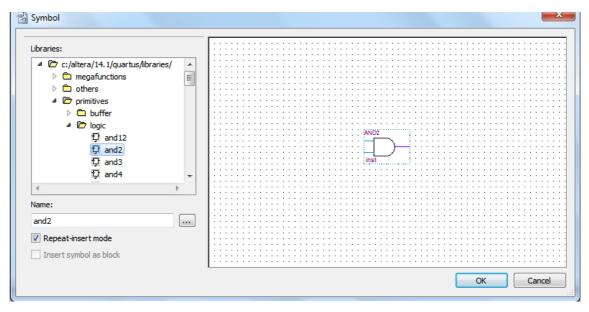

- **2)** Click on  $\bigcirc$  icon and expand the **library** directory and then expand **primitives** directory. In primitives, expand **logic** directory and choose **and2** gate as shown in Fig. 5.

Fig. 5: Choosing a symbol from library

- **3)** Place **and2** gate into the sheet and then choose and place **and3**, **or2** and **not** gates as you choose **and2** gate from the library.

- **4)** Before wiring, **Input and output pins** are needed to be placed. Apply same procedure like choosing a gate but now expand **pin** directory instead of logic directory. Then choose and place **Input and Output** pins respectively.

- **5)** Right click on the input pin at the top of the schematic and choose properties. Write x as pin name and click OK. Do the same thing for the other input and output pins and name the remaining pins as y, z and S respectively.

| Pin Properties                                                                                                                     |  |

|------------------------------------------------------------------------------------------------------------------------------------|--|

| General Format                                                                                                                     |  |

| To create multiple pins, enter a name in AHDL bus notation<br>(For example: "name[30]"), or enter a comma-seperated list of names. |  |

| Pin name(s):                                                                                                                       |  |

| Default value: VCC                                                                                                                 |  |

|                                                                                                                                    |  |

|                                                                                                                                    |  |

|                                                                                                                                    |  |

|                                                                                                                                    |  |

|                                                                                                                                    |  |

|                                                                                                                                    |  |

| OK Cancel Help                                                                                                                     |  |

Fig. 6: Assigning Pin Names

6) Now we are ready to make wiring. Click on [7] (Orthogonal Node Tool) icon. Position the mouse pointer over the right edge of the *x* input pin. Click and hold the mouse button and drag the mouse to the right until the drawn line reaches the pinstub on the top input of the not gate. Release the mouse button when you see a box appear, which leaves the line connecting the two pinstubs. Apply same procedure for remaining wires and construct the circuit shown in Fig. 7. After wiring save the schematic.

Fig. 7: The completed circuit diagram

### c) Compiling the Designed circuit

The entered schematic diagram file, EE314.bdf, is processed by several Quartus II tools that analyze the file, synthesize the circuit, and generate an implementation of it for the target chip. These tools are controlled by the application program called the Compiler.

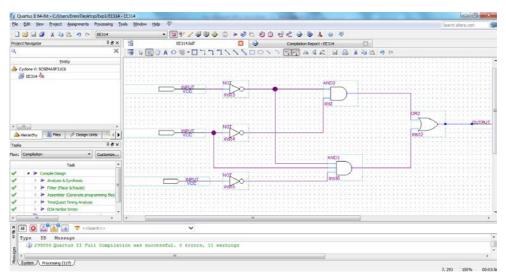

1) Run the compiler selecting Processing > Start Compilation or click on icon. You are supposed to save your project before compiling. As the compilation is continuing, the progress is reported at the left of the schematic. When the compilation finishes, compilation report is produced. A tab showing the report is opened automatically and you can close it. To open it whenever you want, click Processing>Compilation Report. There are several messages are in the message window. When compilation becomes unsuccessful, appropriate messages will be given in there. The interface looks like in Fig. 8 after a successful compilation.

Fig. 8: The screen after a successful compilation

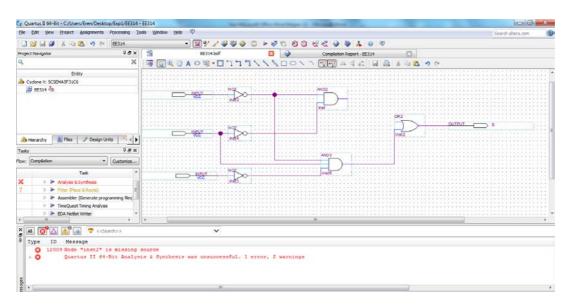

2) Now we will see what happens if the compiler cannot compile the designed circuit. Click on the icon and right click on the wire between **output of and2** and **input of or2 gate** and then click on **Delete**. Then compile your design. You will see a screen similar to the Fig. 9.

Fig. 9: Unsuccessful Compile Screen

**3)** Fix the circuit and recompile your design again.

### d) Pin Assignment

We are supposed to choose input and output pins to be able to test the circuit implemented on FPGA. As input we will use switches and as output we will use a LED.

### 1) Select Assignments>Assignment Editor.

- 2) In the Category drop-down menu, select All. Click on the <<new>> button located near the top left corner to make a new item appear in the Table 2. Double click the box under the column labeled To so that Node Finder button min appears.

- **3)** Click on the button to reach the window in Fig. 10. Click on ≥ to reach more search options. In Filter drop down menu select **Pins: all**. Then click the List button to display output and input pins to be assigned: (S, x, y, z). Click on >> button and click OK. Now all pins are labeled under the column **To**.

| 🥩 Node Fir | der         |              | -                                        |                                                                                                                                                         | 10a - 1         |             | 0.00        |                | x      |

|------------|-------------|--------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|-------------|----------------|--------|

| Named:     | *           |              |                                          |                                                                                                                                                         |                 |             | •           | List           |        |

| Options    |             |              |                                          |                                                                                                                                                         |                 |             |             |                |        |

| Filter:    | Pins: all   |              |                                          |                                                                                                                                                         |                 |             |             | Customize      |        |

| Look in:   | EE314       |              |                                          |                                                                                                                                                         | <b>-</b>        | 🛛 🔽 Include | subentities | Hierarchy view |        |

| Nodes Fou  | ind:        |              | +: =:                                    |                                                                                                                                                         | Selected Nodes: |             |             |                |        |

|            | Name        |              | Assignments                              | ф <b> </b>                                                                                                                                              |                 | Name        |             | Assignments    |        |

|            | 5<br>K<br>Z | Unas<br>Unas | ssigned<br>ssigned<br>ssigned<br>ssigned | $\begin{array}{c} \mathbf{\lambda} \\ \mathbf{\dot{\lambda}} \\ \mathbf{\dot{\lambda}} \\ \mathbf{\dot{\lambda}} \\ \mathbf{\dot{\lambda}} \end{array}$ |                 |             |             |                |        |

| •          |             | III          | •                                        | <b>  </b> 4                                                                                                                                             | •               |             | ОК          | Cancel         | •<br>• |

Fig. 10: Node Finder window

**4)** Now open the drop down menu under **Assignment Name** column and select **Location(Accepts wildcards/group)** as shown in Figure 11.

| Edit View Broject Assignments Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ecols Window Help                         | 10                                   |                                                                                        |                                          |                    |                     |                   | Search altera.com |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------|--------------------|---------------------|-------------------|-------------------|--|

| 😂 🖬 🥔 🕹 🖏 🖏 🤊 (* 🔤 314                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           | · (2) / 4                            | 80 0 × 2 10 0 0                                                                        |                                          | 0.00               |                     |                   |                   |  |

| ct Navigator 0.8 x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           | EE314.bdf                            | C3 🗳                                                                                   | Assignment Editor                        |                    |                     |                   |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                      |                                                                                        |                                          |                    | -                   |                   | Category: All     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tatu From                                 | To                                   | Assignment Name Value                                                                  | Enabled                                  | Entity             | Comment             | Tag               | - Concept Point   |  |

| Entity<br>Cyclone V: SCSEMAS#31C6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                         | 25 S                                 | Location (Accepts widcards.igroups)                                                    | Enabled                                  | Entropy            | Contractic          | iag 🔹             | í -               |  |

| EE314                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 1                                       | B- +                                 | Implement as Clock Enable                                                              |                                          |                    |                     |                   |                   |  |

| 6 EE 314 AM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 1                                       | 3- Y                                 | Implement as Output of Logic Cell<br>Infer RAMs from Raw Logic (Accepts will           | (cande (ormune)                          |                    |                     |                   |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4 1                                       | B- #                                 | Input Termination (Accepts wildcards/or                                                | a.cm)                                    |                    |                     |                   |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5 < <re>Crew&gt;&gt;</re>                 | < <nex>&gt;&gt;</nex>                | Input Transition Time (Accepts wildcards<br>Iteration limit for constant Verilog loops | Accepts wildcards income                 | a.                 |                     |                   |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                      | Iteration limit for non-constant Veriloo k                                             | oos (Accepts wildcards/or                | oups)              |                     |                   |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                      | Keep synchronous clear/preset behavio<br>LVDS Direct Loopback Mode (Accepts wil        | for DDSO INPUT when un<br>dcards/groups) | map 1/0 wysiwyg pr | imitives (Accepts v | vildcards/groups) |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                      | Location (Accepts wildcards/groups)                                                    |                                          |                    |                     | *                 |                   |  |

| Hierarchy 🔝 Files 🖉 Design Units 🕺 🔞                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                         |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

| 0.6×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                         |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

| Compliation • Customize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

| Task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

| Task .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

| 🔺 🏓 Comple Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

| Comple Design     Analysis & Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |

| Comple Design     P Analysis & Synthesis     P Fitter (Race & Route)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |                                      |                                                                                        |                                          |                    |                     |                   |                   |  |